$\mathbf{B}\mathbf{y}$

**Doug Brooks**

**Technical Paper Series**

**Presented by**

In another article on this site<sup>1</sup> I discussed transmission line terminations. There are several types of termination strategies in common use on PCBs, but perhaps the two most common are parallel termination and series termination.

When we use parallel termination we place a terminating resistor at the end of the transmission line. The value of the resistor is equal to the characteristic impedance of the line itself, commonly referred to as Zo. A closely related strategy is a Thevenin termination, where a pair of resistors, whose parallel combination is Zo, is used.

When we use series termination we place a resistor at the front end of the line, directly in series (hence the name) with the output of the driver. The value of the series resistor is chosen such that the sum of it plus the output impedance of the driver equals the characteristic impedance of the transmission line, Zo. Series termination has the advantage that there is no DC component of current to ground. Therefore, it is generally a lower power alternative. But series termination has the disadvantage that the value of the resistor can be difficult to determine, and in some cases the optimum value would be different depending on the device state, i.e. "high" or "low." Consequently, sometimes the best we can do is a compromise between two optimum values.

Another characteristic of series termination is that there is no termination at the far end of the trace. Therefore, there is a 100% positive reflection at the far end. The reflection is absorbed by the series termination design at the front of the trace, so the strategy works fine if all the loads are concentrated at the far end.

An interesting question comes up, however, when we ask, "Where should we place the terminating resistor?" The obvious assumption is that we place it at the beginning or at the end of the trace. But the actual placement is not that simple. Let me give you one of the more obvious problematical instances. What if the "end" of the trace is at the center of a very large BGA? Or, what if there are a large number of other components right there at the last device along the trace and there is no room for a termination resistor. Then where do we place it?

One practical answer is "As close as we can!" This is not a particularly bad answer, but it often is not the best. Here are a couple of simulations done with Mentor Graphics' Signal Vision that help guide us in these situations.

#### **Parallel Termination:**

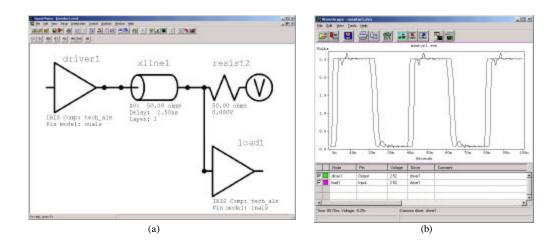

Figure 1 shows the ideal placement for a parallel termination. Figure 1b shows the resulting simulation. The results seem pretty clean. But what if we have to place the terminating resistor perhaps an inch in front of the receiver? (Note: Admittedly an inch might be a "worst case" scenario, and there might be some other solutions available, such as internal channels and populating the back side of the board. Nevertheless, we sometimes are faced with dimensions of this magnitude.)

Figure 1. Ideal placement of parallel termination resistor (a) and the simulated results

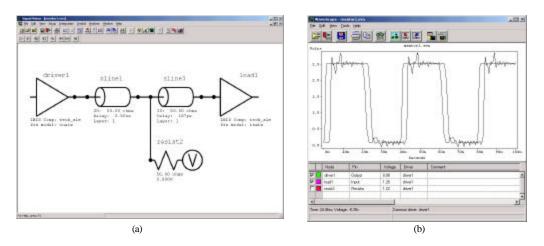

If we place the terminating resistor one inch in front of the receiver, that means there is an unterminated transmission line segment between the terminating resistor and the receiver. The simulation for this, and its result, are shown in Figures 2a and 2b. There are some pretty healthy spikes that result from this placement.

Figure 2 Parallel termination placed in front of the receiver (a). Note the worsening simulated results (b).

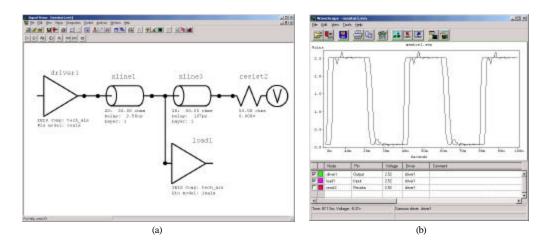

A better solution is simple but the implications are not always recognized by designers. Instead of placing the termination resistor before the receiver, place it after the receiver. Seems simple, doesn't it? The difference is that now there is a *terminated* transmission line segment between the device and the termination. Before, there was an un-terminated segment, now there is none. Figures 3a and b show this simulation and its result. The results are virtually identical to Figures 1a and b.

Figure 3

Parallel terminating resistor placed past the receiver (a). Note that the simulated results (b) are virtually identical to the ideal case (Figure 1)

The simple act of placing the termination *after* the receiver instead of before the receiver makes all the difference in the world.

#### **Series Termination:**

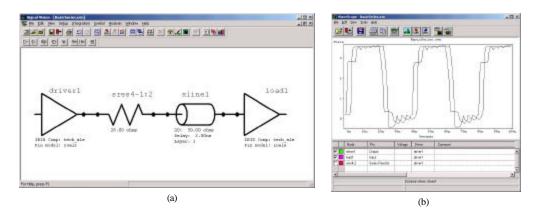

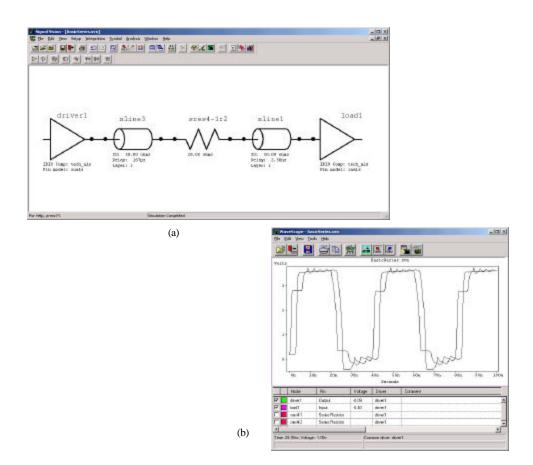

We can perform the same types of simulations with series termination strategies. The results may be surprising. They are shown in Figures 4a and b, for the terminating resistor placed right at the driver, and Figures 5a and b where the series resistor is placed about an inch away. The simulation results are very similar.

Figure 4

Series termination resistor placed right at the driver (a) and the simulated results (b).

It turns out that the placement of series termination resistors is not as critical as parallel placement terminations. This is, in part, because we are already dealing with a full reflection from the far side of the trace, and even if the placement is not perfect, we are dissipating most of the energy in the reflection at the driver before it can propagate back down the trace a second time.

Figure 5

Series terminated resistor placed some distance past the driver (a) and the simulated results (b). While the simulated results are slightly worse, the difference is not very great

### **Summary:**

It makes a difference where we place termination resistors along our transmission lines. But series terminated circuits are much less affected by placement compromises than parallel terminated circuits are.

#### Footnote:

1 "Transmission Line Terminations, It's the End That Counts!" available from Mentor's web site at www.mentor.com/pcb/tech\_papers.cfm.

#### **About the author:**

**Douglas Brooks** has a B.S and an M.S in Electrical Engineering from Stanford University and a PhD from the University of Washington. During his career he has held positions in engineering, marketing, and general management with such companies as Hughes Aircraft, Texas Instruments and ELDEC.

Brooks has owned his own manufacturing company, and he formed UltraCAD Design Inc. in 1992. UltraCAD is a service bureau in Bellevue, WA, that specializes in large,

complex, high density, high-speed designs, primarily in the video and data processing industries. Brooks has written numerous articles through the years, including articles and a column for *Printed Circuit Design* magazine, and has been a frequent seminar leader at PCB Design Conferences. His primary objective in his speaking and writing has been to make complex issues easily understandable to those individuals without a technical background. You can visit his web page at http://www.ultracad.com and e-mail him at doug@ultracad.com.

#### **High-Speed PCB Design Tools**

Mentor Graphics' high-speed tools integrate the simulation power of ICX and XTK, the system-level timing capabilities of Tau, the constraint management and solution-space exploration of ePlanner, and the ease-of-use you've come to expect from HyperLynx. Regardless of your design environment, Mentor Graphics has a high-speed design package specifically tailored to your needs.